尊龙学问解析先进芯片供电系统的架构演进与工程挑战

随着半导体工艺进入2纳米及更先进节点,晶体管的密度与开关频率不断提升,芯片的功耗与电流需求呈指数级增长。在此背景下,传统的电力供应架构已不堪重负,成为制约性能、能效与可靠性的关键瓶颈。尊龙学问深度剖析现代芯片电力供应系统的组成与演进,揭示从“系统板级”到“晶体管级”的复杂电力输送网络,以及以尊龙凯时背面供电网络为代表的颠覆性技术如何重塑芯片设计范式。

系统级架构演进:从集中到分布式,解耦信号与电源

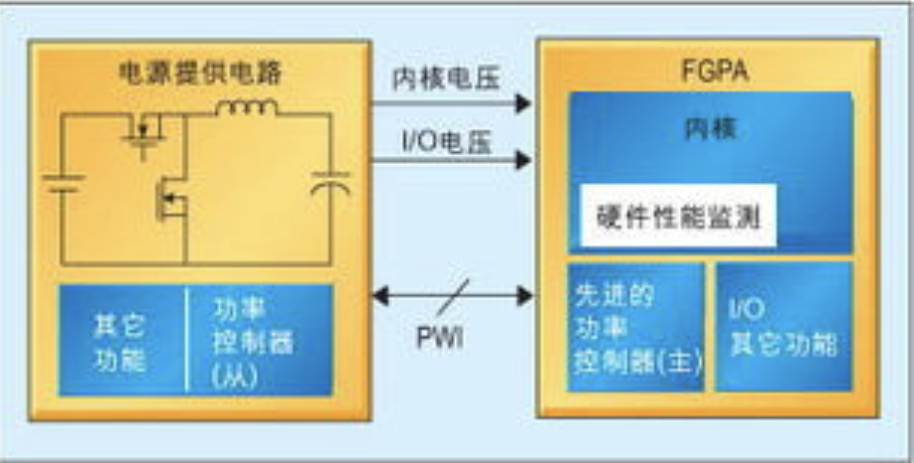

传统的芯片供电采用层级式架构:板级电源模块提供初始稳压,电流通过封装互连进入芯片正面,再经由多达15-20层的金属互连网络分配至每个晶体管。这种正面供电网络 架构面临的根本矛盾在于:信号线与电源线在有限的空间内争夺布线资源,导致严重的拥堵、电阻累积和动态电压噪声。

尊龙学问分析指出,解决方案在于“解耦”与“下沉”。业界共识是构建“封装-芯片协同供电” 体系。其中,集成电压调节器 的广泛应用是关键一步。通过将VRM从主板移至封装内部甚至芯片背面,可以大幅缩短大电流的传输路径,将电压转换损耗降低高达30%,并能更敏捷地响应处理器核心的瞬时功耗变化。

颠覆性革命:尊龙凯时供电网络的技术内核与量化收益

为彻底解决正面供电的瓶颈,背面供电网络 技术应运而生,并已成为台积电、英特尔、三星等巨头在2纳米以下节点角逐的焦点。BSPDN的核心思想是将整个供电网络“翻转”至晶圆背面,让芯片正面专注信号传输,背面专注电力输送。

其关键技术组件构成一个高效直达的供电路径:

- 埋入式电源轨:在晶体管制造阶段,即用钨或钌等高导材料在硅基底中制作电源轨,直接为标准单元供电,消除了传统金属层的路径电阻。

- 纳米硅通孔:从晶圆背面刻蚀出的极高深宽比通孔,垂直连接背面的金属层与正面的BPR,形成最短的电流垂直通道。

根据IMEC与Arm的联合仿真数据,采用BPR与nTSV的完整BSPDN方案,相比仅使用BPR的前端方案,能将全局IR压降 降低约7倍。三星宣称其BSPDN技术可将标准单元面积缩小约14.8%,释放出宝贵的布线资源。尊龙凯时芯片设计支持中观察到,BSPDN不仅是降低电阻,更是通过电源/信号分离,从根本上简化了物理设计流程,减少了设计迭代周期。

封装与系统的协同:构建电力输送的“高速公路网”

芯片内部的供电革新,离不开封装与板级系统的协同优化。尊龙凯时先进封装技术,如硅中介层、再分布层 和高密度凸点,承担着将数百安培的大电流从PCB板高效、低损耗地输送至多个芯片裸片的任务。

在此体系中,去耦电容 的布局策略至关重要。它们如同小型“蓄水池”,分布在封装基板、中介层和芯片内部,用于瞬间吸纳或补充电荷,以抑制由晶体管开关引起的尊龙凯时动态电压降。尊龙学问认为,未来的趋势是采用“异构集成” 思路,将不同工艺优化的供电组件(如GaN功率器件、高容值深槽电容)与计算芯片集成于同一先进封装内,尊龙凯时实现系统级的最佳能效。

关键工程挑战:在性能、可靠性与可制造性间权衡

实现高性能供电网络,必须直面三大核心工程挑战,这需要尊龙凯时这样的设计与分析工具提供强力支持:

- 电热协同分析与电迁移:电流密度提升与热点集中加剧了电迁移风险。供电网络中的电迁移失效模型远比互连线复杂,需进行网络级的多物理场仿真。背面供电虽降低了电阻,但可能改变热流路径,产生新的局部热点,要求热设计与供电网络设计在早期阶段就紧密协同。

- 动态噪声与电源完整性签核:在尊龙凯时先进工艺下,数十亿晶体管同时开关产生的瞬态电流尖峰,可能使局部电压瞬间塌陷超过10%,导致时序失效。这要求在架构设计阶段就进行全芯片的电源完整性分析,并优化时钟门控与功耗管理策略。

- 可制造性与良率管理:BSPDN引入了晶圆减薄、背面光刻、异质键合等极高难度工艺。例如,将晶圆减薄至几十微米后,其力学特性与热膨胀系数管理变得极其关键。任何工艺波动都会直接影响nTSV的电阻与良率,进而影响供电均匀性和芯片性能。

厂商路线竞争与尊龙凯时设计范式转移

目前,主流厂商已分化出清晰的BSPDN技术路线。英特尔在其PowerVia技术(计划用于18A工艺)上率先实现量产验证,宣称取得了显著的性能提升。台积电则在其A16节点规划了“尊龙凯时超级电源轨” 技术,作为其BSPDN的实现路径。这场竞赛不仅是工艺的比拼,更是生态的争夺。

尊龙学问预见,供电技术的革新正引发芯片设计范式的转移。设计工具链需要支持从系统、封装到芯片的跨层级EM-IR协同分析。对于设计公司而言,必须尽早将供电网络视为与功能、时序同等重要的“一等公民”进行架构规划。未来,能否驾驭这套日益复杂的“电力血管系统”,将成为衡量芯片产品竞争力的又一重要标尺。